# Ultra Low Frequency Low Power CMOS Oscillators for MPPT and Switch Mode Power Supplies

Francarl Galea<sup>1</sup>, Owen Casha, Ivan Grech, Edward Gatt and Joseph Micallef

Department of Microelectronics and Nanoelectronics

University of Malta

<sup>1</sup>Email: francarl.galea@um.edu.mt

Abstract—This paper presents the design of two low power consumption analog oscillators implemented in a 0.35 µm CMOS technology. These oscillators were designed for a power conditioning circuit with an analogue Perturbation and Observation (P&O) Maximum Power Point Tracker (MPPT) to maximize the scavenged power generated by energy harvesting devices. The nominal frequency of the two oscillators is 15 Hz and 200 kHz, respectively. The 15 Hz oscillator is used to clock the MPPT, whereas the second oscillator generates a sawtooth wave required for the Pulse Width Modulation (PWM) of the switch mode converter. Both oscillators work with a supply voltage of 1V and use a reference current generated by a self-biasing zero temperature coefficient circuit. All the circuitry was designed to operate in the sub-threshold region in order to keep its power consumption to a minimum. The frequency of the 15 Hz oscillator varies by 7.1% over a temperature variation from -40 °C to 125 °C. The total power consumption including the current reference circuit is 30 nW at 27 °C and reaches a maximum of 90 nW at 80 °C. The frequency of the 200 kHz oscillator varies by 33% over a temperature variation from -40 °C to 125 °C. The sawtooth generator, together with the current reference circuit, consume 63 nW across this temperature range.

# I. INTRODUCTION

Various applications require low frequency oscillators as part of their circuitry. Cardiac pacemakers, navy and submarine radio communication, MPPT circuits, sensor monitoring circuits, and low power switch mode converters all require a low frequency clock signal which has to be generated by ultra low frequency oscillators [1], [2].

The conventional CMOS ring oscillator generates a frequency in the order of MHz [3], [4]. To produce a lower frequency signal of the order of hundreds of Hz, frequency dividers have to be employed. Although this method is capable to accurately generate its designated frequency, its main drawback is the high static power consumption. Alternative circuit topologies, such as relaxation oscillators, exist but they are not capable of generating low frequency signals unless very large off-chip passive components are used [5].

An ultra low frequency ring oscillator using the concept of CMOS thyristors, was designed in [6]. The drawbacks of this oscillator are that it requires a minimum supply voltage of 2.5 V, occupies a considerable area since it requires three capacitors and dissipates a static power of  $5.7 \mu \text{W}$ .

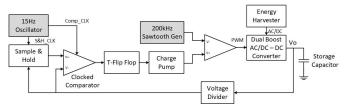

This paper presents the design of two low power consumption analog oscillators to be employed in a charge conditioning MPPT circuit for energy harvesting applications [2]. Both

Fig. 1: Schematic diagram of the MPPT Charge Controller [2].

oscillators require only one capacitor and work with a supply voltage of 1 V. Such a low supply voltage is beneficial so that the MPPT can operate once the voltage generated by the energy harvester exceeds 1 V. The schematic diagram of the charge controller is shown in Fig. 1. The 15 Hz oscillator provides a clock signal to both a sample and hold (S&H) circuit and to a clocked comparator, which are essential to implement the P&O MPPT algorithm. The 200 kHz sawtooth generator is required to generate the PWM of an improved version dual boost converter, which is able to directly convert an AC input voltage to a DC output voltage without full wave rectification [7]. The power consumption of the sawtooth generator is very low and may also be used to generate PWM signals for other types of switch mode converters and power supplies. The frequency and duty cycle of the designed oscillators is controlled by means of a reference current, generated by a sub-threshold zero temperature coefficient self biasing circuit.

## II. Design of the $15 \,\mathrm{Hz}$ Oscillator

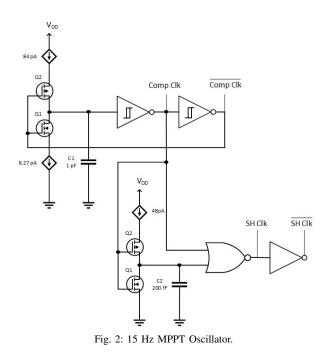

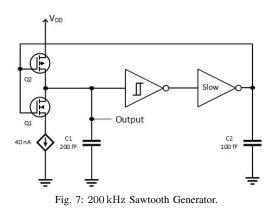

For the application described above [2], a low precision low power consumption oscillator is required. This oscillator is implemented by looping two Schmitt inverters to a current starved inverter, as shown in Fig. 2. It generates a clock signal of 15 Hz. The current starved inverter charges and discharges the 1 pF timing capacitor *C1* and uses  $1149 \,\mu\text{m}^2$  of area. The current which charges and discharges capacitor *C1* is set via two current mirrors.

The frequency and duty cycle of the generated clock pulses are determined by the current of the inverter, the capacitance of C1 and the hysteresis values of the Schmitt inverter. The charging time of C1 determines the clock pulse width, whereas the discharging time of C1 determines the periodic time of the clock. In order for the clock frequency not to drift with temperature and voltage variations, a self biasing circuit generating a reference current was employed.

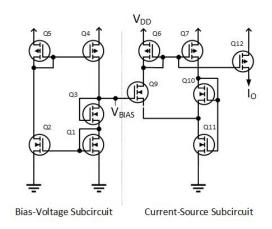

A zero temperature coefficient CMOS current reference circuit consisting of subthreshold transistors was designed [8]. This circuit consists of a self biased voltage reference subcircuit which generates the voltage  $V_{BIAS}$  to bias the current-source subcircuit. The former exhibits a positive temperature coefficient, whereas the current source subcircuit exhibits a negative temperature coefficient, resulting in a net zero temperature coefficient output current. Practical results show that this circuit consumes a power of 1µW [8]. The MPPT circuit without the reference current consumes  $250 \,\mathrm{nW}$ [2] and therefore the reference current circuit proposed in [8] consumes too much power for this application. In order to consume less power, the circuit was modified as shown in Fig. 3. The bias-voltage subcircuit was redesigned to require only a self-biased Wilson current mirror [9]. To reach the required bias voltage for Q9 with smaller currents, the diode connected transistor Q3 was added. Analysis of this circuit vields:

$$I_O = I_{D_0} K_9 \left(\frac{K_1 K_{11}}{2K_2 K_{10}}\right)^2 e^{\frac{2V_{GS3} + \delta V_{TH}}{nV_t}} \tag{1}$$

where  $\delta V_{TH} = V_{T_2} + V_{T_{11}} - V_{T_3} - V_{T_9} - V_{T_{10}}$  and K is the transistor aspect ratio.

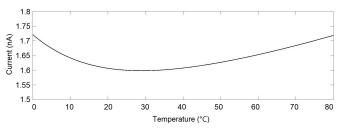

From Eq. 1, it can be deduced that the thermal coefficient of the output current can be minimized through appropriate adjustment of the threshold voltages of Q2, Q3, Q9, Q10 and Q11. This can be achieved by appropriate sizing. The reference current circuit designed for the oscillator consumes a power of 7.6 nW at a temperature of 27 °C. The current output variation with temperature is presented in Fig. 4.

The clock pulses supplied to the clocked comparator should be of at least 2 ms for the comparator and the TFF to carry out their operation. The comparator is designed with low bias currents for minimal power dissipation resulting in a low slew

Fig. 3: Self-biasing temperature independent current reference circuit.

Fig. 4: Variation of the current reference output with temperature.

rate. In order to give allowance due to temperature and process variations, the oscillator was designed to have a pulse width of 5 ms. The hystheresis limits of the designed Schmitt inverter are of 180 mV and 600 mV. Hence using  $I = C \frac{\delta V}{\delta t}$  the charging current and discharging current are calculated to be 84 pA and 6.27 pA, respectively.

This 15 Hz oscillator also generates the clock pulses to the S&H circuit as shown in Fig. 1. This clock pulse is applied exactly once the comparator's clock pulse is over and should be of at least  $500 \,\mu\text{s}$  wide for the S&H's capacitor to charge or discharge to the input voltage.

This pulse is generated by the lower part of the circuit in Fig. 2. When Comp\_Clk is at 1 V, capacitor C2 discharges through transistor Q1 and so the output of the NOR Gate which drives the S&H goes low. As soon as Comp\_Clk is low, the NOR Gate's output goes high initiating the S&H clock pulse. Consequently, capacitor C2 starts charging with a current of 48 pA via another current mirror from the same reference current circuit. Once it charges to 340 mV, which is considered a high signal by the NOR gate, the NOR Gate's output goes back to low.

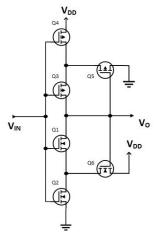

The Schmitt inverter, shown in Fig. 5, uses four stacked transistors to invert the input signal and two additional transistors, Q5 and Q6, to feedback the output voltage [10] [11] to alter the threshold voltage of the inverter depending on the current state of the inverter. The aspect ratio of transistors Q2 and Q6 where adjusted to obtain the upper limit voltage  $(V_{IH})$  required and the aspect ratio of transistors Q5 and Q4 was adjusted to achieve the lower limit voltage  $(V_{IL})$  required.

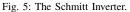

The oscillator was simulated at various temperature con-

Fig. 6: 15 Hz Oscillator Timing Capacitors Voltages and Comparator and Sample & Hold Clock Pulses Plots

ditions. The results of the optimized design and its power dissipation (including reference current circuit) are listed in Table I. Corner analysis and Monte Carlo simulations were carried out to obtain a robust design. The frequency may drift from 14 Hz to 20 Hz when simulating with both temperature and process variations. Monte Carlo simulations resulted in a standard deviation of 6 Hz. The offset of the oscillator output frequency from the nominal 15 Hz are not expected to affect the operation of the MPPT circuit. Table II compares the performance of the proposed oscillator with the state of the art (SOA). The temperature coefficient and voltage coefficient of

TABLE I Performance of the 15 Hz oscillator across different temperatures.

| Temp.                   | Frequency | Comp. Pulse | S&H Pulse        | Cons.           |

|-------------------------|-----------|-------------|------------------|-----------------|

| 0°C                     | 16 Hz     | 6.3 ms      | $1.5\mathrm{ms}$ | $15\mathrm{nW}$ |

| $27 ^{\circ}\mathrm{C}$ | 15 Hz     | 5.5 ms      | $1.2\mathrm{ms}$ | $30\mathrm{nW}$ |

| $80^{\circ}\mathrm{C}$  | 16 Hz     | 3.8 ms      | $0.8\mathrm{ms}$ | $90\mathrm{nW}$ |

TABLE II Comparison of the  $15\,\mathrm{Hz}$  oscillator with the SOA.

| Reference | Technology   | Min. Supply<br>Voltage | Frequency | Power      |

|-----------|--------------|------------------------|-----------|------------|

| [1]       | 180 nm CMOS  | 2.5 V                  | 0.303 Hz  | 6.6nW      |

| [6]       | 250 nm CMOS  | 2.5 V                  | 8.94 Hz   | $5.7\mu W$ |

| [12]      | 2 µm CMOS    | 2 V                    | 100 Hz    | $0.3\mu W$ |

| This Work | 0.35 µm CMOS | 1 V                    | 15 Hz     | 30nW       |

this oscillator are  $0.27 \%/^{\circ}$ C and  $-0.069 \%/^{\circ}$ C respectively. The area usage of this oscillator including the 200 fF capacitor required to generate the S&H clock pulse is of  $1645 \,\mu\text{m}^2$ .

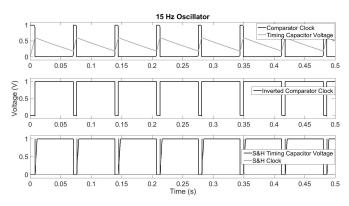

#### III. DESIGN OF THE 200 kHz Sawtooth Generator

The sawtooth generator, shown in Fig. 7, is required to generate a PWM signal to control the switch mode boost converter. It generates a sawtooth waveform with a signal swing which goes from 0 V to 1 V at a frequency of 200 kHz. The circuit consists of a current starved inverter followed by a Schmitt inverter and a NOT gate designed to have a low output slew rate. The current starved inverter uses a current source in order to precisely control the rate at which the 200 fF timing capacitor *C1* is discharged.

The sawtooth output voltage wave is generated across the timing capacitor CI. The implemented Schmitt inverter circuit is shown in Fig. 5. It is designed to have a  $V_{IL}$  as close to 0 V as possible and, since the NOT gate has a low slew rate and a capacitive load of 100 fF, the current starved inverter would continue discharging capacitor CI for 50 ns after the Schmitt inverter changes its state. The timing capacitor is charged in 20 ns which is less than 1% of the full cycle. Hence, the frequency of the oscillator is mainly determined by the discharging current, the timing capacitor and the hysteresis values of the Schmitt inverter, which are 0 V and 1 V.

A discharging current of 40 nA is required to achieve an oscillation frequency of 200 kHz. This current is set by mirroring a current from a self biased temperature independent reference current circuit, similar to the one shown in Fig. 3 and consumes 2.5 nW. It was ensured that the sawtooth waveform reaches the maximum value of the charge pump output voltage (1 V) at all operating temperatures and corner conditions, in order to prevent the output duty cycle from reaching 100%. Additionally, it was ensured that, across various process and temperature variations, the sawtooth generator does not have a dead band at 0 V, as this limits the lowest PWM duty cycle which can be obtained, thus limiting the operation of the boost converters at specific input and output voltages which require a low duty cycle. It is preferable that the sawtooth wave does not reach 0 V rather than having a dead-band at 0 V. The Schmitt inverter, similar to the one shown in Fig. 5, was designed to have  $V_{IL} = 90 \,\mathrm{mV}$  in typical conditions, by adjusting the aspect ratios of transistors Q4 and Q5.  $V_{IH}$  was set to

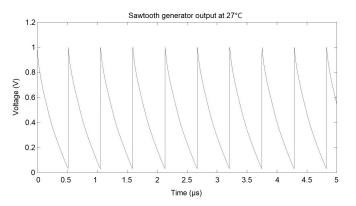

Fig. 8: Transient response of the Sawtooth Generator.

TABLE III Performance of the 200 kHz Sawtooth Oscillator across Different temperatures.

| Temp.                   | Frequency | Dead-band<br>@ 0 V | Minimum<br>Voltage | Maximum<br>Voltage |

|-------------------------|-----------|--------------------|--------------------|--------------------|

| 0 °C                    | 180 kHz   | 0 µs               | 10.7 mV            | 998 mV             |

| $27^{\circ}\mathrm{C}$  | 190 kHz   | $0  \mu s$         | 37.5 mV            | 998 mV             |

| $80 ^{\circ}\mathrm{C}$ | 200 kHz   | $0  \mu s$         | 80 mV              | 999 mV             |

800 mV in typical conditions. This was achieved by adjusting the aspect ratios of transistors Q2 and Q6. The output of the sawtooth generator simulated at  $27 \text{ }^{\circ}\text{C}$  with typical conditions is shown in Fig. 8.

The design of the oscillator was simulated and tested across various temperature conditions. The simulated results are presented in Table III, showing that no dead-band occurs neither at 1 V nor at 0 V. Corner analysis and Monte Carlo simulations were also carried out. Corner analysis with temperature variations resulted in the oscillator frequency to fluctuate from 140 kHz to 220 kHz. Monte Carlo simulations calculated a standard deviation of 34 kHz. Although the 200 kHz oscillator frequency is the ideal switching frequency for the boost converter in the MPPT circuit, variations in this frequency would only affect the switching losses and the ripple currents of the boost converter. The temperature coefficient and voltage coefficient of the proposed oscillator are 0.17 %/°C and 0.029 %/°C respectively and the circuit consumes an area of  $436 \,\mu m^2$ . Table IV compares the specifications of the proposed oscillator with that of existing designs.

### **IV. CONCLUSION**

Simulation results have shown that the frequency of the 15 Hz oscillator varies by 7.1 % over a temperature variation from -40 °C to 125 °C. The total power consumption, including that of the self-bias zero temperature coefficient current reference circuit, is  $30 \,\mathrm{nW}$  at  $27 \,^{\circ}$ C and reaches a

TABLE IV Comparison of the 200 kHz oscillator with the SOA.

| Reference | Technology   | Min. Supply<br>Voltage | Frequency | Power       |

|-----------|--------------|------------------------|-----------|-------------|

| [5]       | 65 nm CMOS   | 1.5 V                  | 18.5 kHz  | 120 nW      |

| [13]      | 0.35 µm CMOS | 1 V                    | 80 kHz    | $1.14\mu W$ |

| [14]      | 65 nm CMOS   | 1.05 V                 | 100 kHz   | $41\mu W$   |

| [15]      | 0.35 µm CMOS | 1.2 V                  | 200 kHz   | $84\mu W$   |

| This Work | 0.35 µm CMOS | 1 V                    | 200 kHz   | 63 nW       |

maximum of 90 nW at 80 °C. The frequency of the 200 kHz sawtooth oscillator varies by 33 % over a temperature variation from -40 °C to 125 °C. The sawtooth generator together with the current reference circuit consume 63 nW, which remains constant throughout all temperature range. The variations due to temperature, in the sawtooth wave particularly the minimum voltage, as listed in Table III were found to be negligible and do not affect the operation of the switch mode converter and its controller.

#### ACKNOWLEDGEMENTS

The research work disclosed in this publication is funded by the ENDEAV-OUR Scholarship Scheme (Malta). The scholarship may be part-financed by the European Union European Social Fund (ESF) under Operational Program II Cohesion Policy 2014-2020, Investing in human capital to create more opportunities and promote the wellbeing of society.

#### REFERENCES

- V. R. Kanth and K. N. Kumar, "Low power and low frequency cmos ring oscillator design," *European Journal of Advances in Engineering* and Technology, vol. 2, no. 7, pp. 82–87, 2015.

- [2] F. Galea, E. Gatt, O. Casha, I. Grech, and J. Micallef, "A CMOS MPPT Power Conditioning Circuit for Energy Harvesters," *ICECS 2017*, 2017.

- [3] J. Eusébio, L. B. Oliveira, L. M. Pires, and J. P. Oliveira, "A 0.5 V Ultra-low Power Quadrature Ring Oscillator," in *Doctoral Conference* on Computing, Electrical and Industrial Systems. Springer, 2014, pp. 575–581.

- [4] W. S. T. Yan and H. C. Luong, "A 900-MHz CMOS low-phase-noise voltage-controlled ring oscillator," *IEEE Transactions on circuits and* systems II: analog and digital signal processing, vol. 48, no. 2, pp. 216–221, 2001.

- [5] A. Paidimarri, D. Griffith, A. Wang, A. P. Chandrakasan, and G. Burra, "A 120nW 18.5 kHz RC oscillator with comparator offset cancellation for±0.25% temperature stability," in *Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International.* IEEE, 2013, pp. 184–185.

- [6] A. K. Mahato, "Ultra low frequency CMOS ring oscillator design," in Engineering and Computational Sciences (RAECS), 2014 Recent Advances in. IEEE, 2014, pp. 1–5.

- [7] G. D. Szarka, S. G. Burrow, and B. H. Stark, "Ultralow power, fully autonomous boost rectifier for electromagnetic energy harvesters," *IEEE Transactions on Power Electronics*, vol. 28, no. 7, pp. 3353–3362, 2013.

- [8] K. Ueno, "CMOS Voltage and Current Reference Circuits consisting of Subthreshold MOSFETs-Micropower Circuit Components for Power-Aware LSI Applications-," in *Solid state circuits technologies*. InTech, 2010.

- [9] G. Palumbo, "Design of the Wilson and improved Wilson MOS current mirrors reach the best settling time," in *Circuits and Systems*, 1994. *ISCAS'94.*, 1994 IEEE International Symposium on, vol. 5. IEEE, 1994, pp. 413–416.

- [10] N. Lotze and Y. Manoli, "A 62 mV 0.13 μm CMOS Standard-Cell-Based Design Technique Using Schmitt-Trigger Logic," *IEEE journal* of solid-state circuits, vol. 47, no. 1, pp. 47–60, 2012.

- [11] C. Zhang, A. Srivastava, and P. Ajmera, "Low voltage CMOS Schmitt trigger circuits," *Electronics Letters*, vol. 39, no. 24, pp. 1696–1698, 2003.

- [12] C. Hwang, S. Bibyk, M. Ismail, and B. Lohiser, "A very low frequency, micropower, low voltage CMOS oscillator for noncardiac pacemakers," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 42, no. 11, pp. 962–966, 1995.

- [13] G. De Vita, F. Marraccini, and G. Iannaccone, "Low-voltage low-power CMOS oscillator with low temperature and process sensitivity," in *Circuits and Systems, 2007. ISCAS 2007. IEEE International Symposium* on. IEEE, 2007, pp. 2152–2155.

- [14] F. Sebastiano, L. J. Breems, K. A. Makinwa, S. Drago, D. M. Leenaerts, and B. Nauta, "A low-voltage mobility-based frequency reference for crystal-less ULP radios," *IEEE journal of solid-state circuits*, vol. 44, no. 7, pp. 2002–2009, 2009.

- [15] K. Lasanen and J. Kostamovaara, "A 1.2-V CMOS RC oscillator for capacitive and resistive sensor applications," *IEEE transactions on instrumentation and measurement*, vol. 57, no. 12, pp. 2792–2800, 2008.